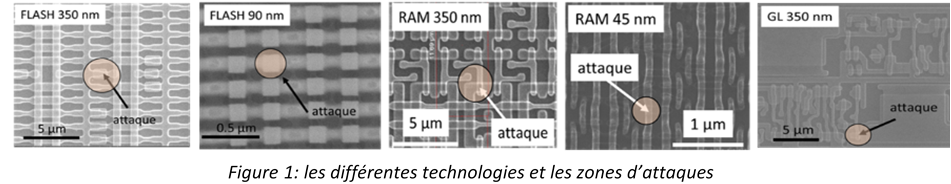

Objectif : L'objectif principal de ce WP est de mener des attaques de plus en plus complexes sur source RX de laboratoire sur différentes technologies. Pour chacune de ces technologies, il faudra éventuellement se localiser sur le ou les transistors à attaquer, réaliser des masques pour protéger le circuit et mener à bien l'attaque. Ces étapes sont plus ou moins compliquées en fonction des technologies et des informations dont nous pouvons disposer ou non sur le circuit : par exemple connaissance ou non du schéma de localisation des transistors (fichiers GDS2) ou nécessité d'une rétro-conception. Enfin, selon les technologies (voir Figure 6), nous attaquerons la mémoire Flash, SRAM ou la Glue logique.

Dans chaque cas, les attaques seront menées in operando. Il s'agira de plus de tester l'efficacité des contre-mesures matérielles et logicielles implémentées dans le WP3 et de valider les simulations menées dans le WP4 (Tâche 4.3). Les différentes tâches sont présentées par la suite.

Tâche 2.1 : Alignement échantillon / faisceau RX / caches fixes ou amovibles / caractérisation faisceau X: Un point important va être le positionnement de l'échantillon par rapport aux rayons X notamment quand la taille des trous dans les caches sera inférieure au micron, la réalisation et l'alignement de cache amovible. Les potentialités d'imagerie qu'offre le tomographe seront particulièrement utiles pour cette phase.

Etape 1 : orientation des échantillons avec cache fixe déposé au FIB : le trou sur le circuit qui laisse passer RX sera orienté perpendiculairement aux rayons X doit être avec les hexapodes de précision de PI[1] qui disposent de précision angulaire au µrad et de 0.2 µm en déplacement XYZ. Comme la durée d'exposition afin de créer des fautes est de plusieurs minutes (voir preuve concept), cela laisse le temps de bien aligner l'échantillon à partir des radios et des plots de contacts : la Figure 1a et la Figure 1b montrent les plots visibles sur un composant 28 nm à différentes résolutions sur des radios prises en 1 s.

Etape 2 : réalisation de caches amovibles pour attaque sans dépôt FIB sur échantillon : des caches en plaque de W de 150 µm d'épaisseur seront percés au FIB pour obtenir des tailles de spot RX sur l'échantillon 2.5 µm, 0.5 µm, 0.25 µm, 0.2 µm pour pouvoir attaquer toutes les technologies de ce projet et les différentes zones (Flash, RAM, Glue Logique).

Etape 3 : centrage des caches amovibles par rapport au faisceau et l'échantillon : les caches seront positionnés devant la source RX avec un moteur XY piézoélectrique et l'échantillon précisément positionné devant le cache avec l'hexapode à partir des zones préalablement localisées avec le FIB ou le GDS2 (Figure 7c).

Etape 4 : caractérisation faisceau X et spot RX sur échantillon : nous caractériserons le spectre en énergie RX obtenu à 100 kV et avec une cible Mo à support diamant avec le spectromètre acquis récemment au laboratoire SIMAP qui constitue une donnée d'entrée importante pour la simulation du WP4.

Tâche 2.2 : Attaque dans la Flash

L'objectif de cette tâche est de simplifier les moyens nécessaires pour faire les attaques en s'affranchissant du synchrotron et du FIB sur une technologie 350 nm (étape 1 à 4) et sur une technologie 90 nm (étape 1 à 3).

Etape 1 : attaque aléatoire au FIB dans la Flash avec cache fixe réalisé : nous utiliserons le dispositif présenté sur la Figure 3 et la méthode utilisée pour la preuve de concept avec des trous de 2.5 µm de diamètre (techno 350 nm) et 0.35 µm (techno 90 nm).

Etape 2 : attaque aléatoire dans la Flash avec cache amovible sans FIB: nous nous mettrons en face arrière pour positionner l'échantillon au plus près du cache en W percé de trous de 500 nm (techno 350 nm) et des trous de 50 à 100 nm (techno 90 nm). Nous utiliserons alors l'hexapode pour déplacer le composant relativement au cache jusqu'à produire des fautes.

Etape 3 : attaque localisée dans la Flash avec cache fixe réalisé au FIB : La localisation se fera au FIB sur la face avant par repérage des coordonnées via un deprocessing au FIB. Le dépôt de W et son perçage seront faits sur la zone choisie. L'attaque sera similaire à l'étape 1 et sera menée sur les deux technologies 350 et 90 nm.

Etape 4 : attaque localisée dans la Flash avec cache amovible et usage limité du FIB : Le FIB sera utilisé pour repérer les coordonnées du transistor par rapport aux plots de contact du composant. Il sera alors possible de positionner l'échantillon en face arrière correctement sur le cache centré sur la cible du tomographe (tâche 2.1 étape 2) avec l'hexapode. L'attaque sera similaire à l'étape 1 et sera menée sur les deux technologies 350 et 90 nm.

Tâche 2.3 : Attaque dans la RAM

Pour les attaques dans la RAM (voir Figure 6), il est nécessaire de localiser les transistors que l'on veut attaquer et donc seules deux étapes sont proposées.

Etape 1 : attaque localisée dans la RAM avec cache fixe réalisé au FIB : la localisation se fera au FIB comme dans le W2.1 pour les technos 350 et 45 nm. Pour le 28nm et 22 nm nous utiliserons le GDS2 pour nous localiser en le superposant à l'image FIB. La mise en œuvre de l'attaque sur le tomographe de laboratoire sera similaire à l'étape 1 de la tâche 2.1.

Etape 2 : attaque localisée dans la RAM avec cache amovible sans FIB : Nous disposons du GDS2 pour le 28 et le 22 nm pour localiser précisément les transistors par rapport aux plots de contacts et aux bords de l'échantillon (voir Figure 7a, Figure 7b, Figure 7c et tâche 2.1). Une fois le cache en W positionné sur la cible (voir la tâche 2.1 étape 2), nous positionnerons l'échantillon aux coordonnées voulues grâce à l'hexapode et nous pourrons mener différentes attaques en bougeant l'échantillon par rapport au cache.

Tâche 2.4 : Attaque dans la Glue logique

Pour les attaques dans la Glue Logique, il est aussi nécessaire de localiser les transistors que l'on veut attaquer. La Figure 6 présente les images MEB de la Glue Logique pour une technologie 350 nm qui montre que le trou pour mener une attaque peut être au plus de 2.5 µm de diamètre soit environ 8 fois la taille de la technologie. Pour des technos plus avancées, il faudra envisager des tailles de trous de l'ordre de 0.22, 0.18 µm pour les technologies de 28 nm, 22 nm.

Etape 1 : attaque localisée dans la Glue Logique avec cache fixe réalisé au FIB : pour le 350 nm, nous nous appuierons sur la rétro-conception qui aura été réalisée dans le WP1 pour se localiser sur les bons transistors. Pour les technologies 28 et 22 nm, la localisation se fera à l'aide du GDS2. Le principe d'attaque sera similaire à celui de la tâche 2.2 (étape 1).

Etape 2 : attaque localisée dans la Glue Logique avec cache amovible et usage limité du FIB : nous reproduirons dans la Glue Logique la même démarche que pour la RAM en nous limitant aux technologies 28 et 22 nm pour lesquelles nous disposons du GDS2.

[1] https://www.pi-usa.us/en/products/6-axis-hexapods-parallel-positioners/h-811i2i2v-6-axis-miniature-hexapod-700886/#description